# 指令格式与译码

# 指令字段

所有指令均为 32 位,根据不同指令类型,字段分布和功能如下:

| 字段名 | 位范围 | 位数 | 功能描述 | 适用指令类型 |

|---|---|---|---|---|

| Instruction | 31:0 | 32 | 32 位指令 | R/I/J |

| Op | 31:26 | 6 | 操作码 | R/I/J |

| Rs | 25:21 | 5 | 源寄存器 | R/I |

| Rt | 20:16 | 5 | 源/目标寄存器 | R/I |

| Rd | 15:11 | 5 | 目标寄存器 | R |

| Shamt | 10:6 | 5 | 移位量 | R |

| Func | 5:0 | 6 | 功能码 | R |

| Imm16 | 15:0 | 16 | 16 位立即数 | I |

| Target addr | 25:0 | 26 | 26 位目标地址 | J |

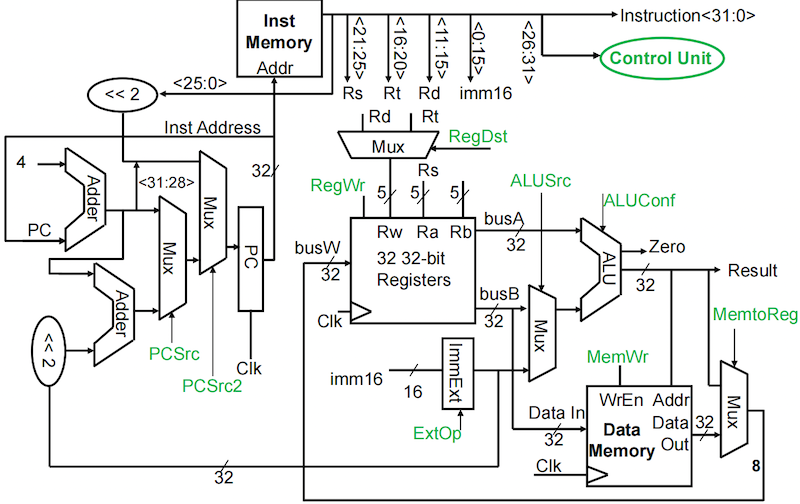

# 单周期处理器设计

# 关键路径与执行阶段

单周期处理器中,不同指令类型完成执行所需的阶段如下:

| 指令类型 | 指令获取 (IF) | 指令译码/寄存器读取 (ID/RF) | 执行 (EX) | 存储器访问 (MEM) | 结果写回 (WB) |

|---|---|---|---|---|---|

| R 型 | 1 | 1 | 1 | - | 1 |

| Load | 1 | 1 | 1 | 1 | 1 |

| Store | 1 | 1 | 1 | 1 | - |

| Branch | 1 | 1 | 1 | - | - |

| 其余 I 型 | 1 | 1 | 1 | - | 1 |

| Jump | 1 | 1 | - | - | - |

# 控制信号

单周期处理器中的控制信号及其功能:

| 信号名 | 功能描述 | 备注 |

|---|---|---|

| PCSrc(/2) | 程序计数器方式控制 | 0 - 顺序执行,1 - 分支跳转 (beq/J) |

| Branch | 是否是 beq 指令 | 0 - 不是,1 - 是 |

| ExtOp | 立即数扩展方式控制 | 0 - 补零,1 - 符号扩展 |

| ALUSrc | ALU 第二个输入选择 | 0 - regB,1 - imm32 |

| ALUConf | ALU 运算类型选择 | add, sub, or 等 |

| MemWr | 存储器写入使能 | 0 - 禁用,1 - 启用 |

| MemtoReg | 寄存器写入数据源选择 | 0 - ALU 结果,1 - 存储器数据 |

| RegDst | 写入寄存器选择 | 0 - Rt,1 - Rd |

| RegWr | 寄存器写入使能 | 0 - 禁用,1 - 启用 |

# 指令控制信号表

不同指令在单周期处理器中的控制信号配置:

| 信号名 | add | sub | lw | sw | beq | ori | jump |

|---|---|---|---|---|---|---|---|

| PCSrc | 0 | 0 | 0 | 0 | Zero | 0 | 1 |

| PCSrc(2) | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| Branch | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| ExtOp | - | - | 1 | 1 | 1 | 0 | - |

| ALUSrc | 0 | 0 | 1 | 1 | 0 | 1 | - |

| ALUConf | Add | Sub | Add | Add | Sub | Or | - |

| MemWr | 0 | 0 | 0 | 1 | 0 | 0 | 0 |

| MemtoReg | 0 | 0 | 1 | - | - | 0 | - |

| RegDst | 1 | 1 | 0 | - | - | 0 | - |

| RegWr | 1 | 1 | 1 | 0 | 0 | 1 | 0 |

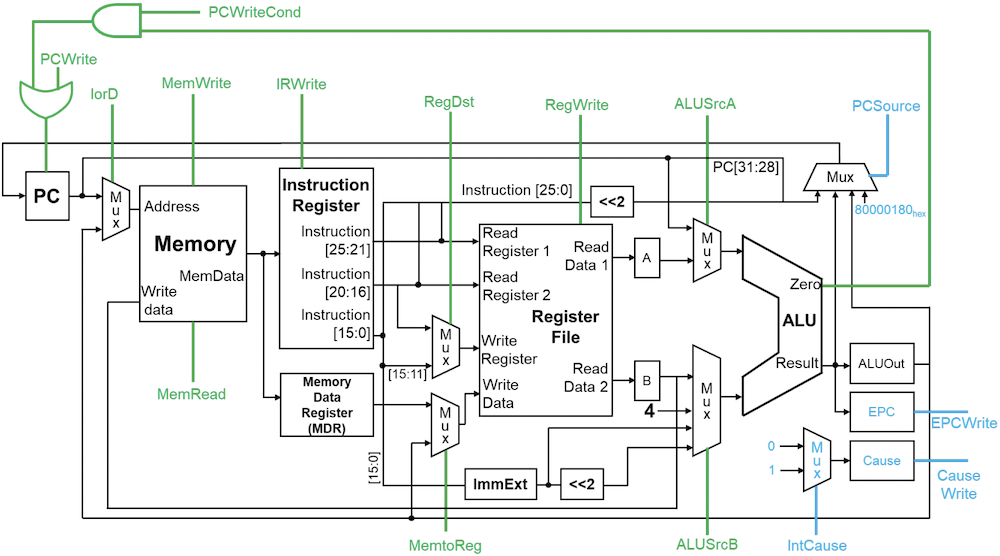

# 多周期处理器设计

# 阶段描述与操作

多周期处理器将指令执行分为多个阶段,每个阶段完成特定的操作:

| 阶段 | R 型 | Load | Store | Branch | 其余 I 型 | Jump |

|---|---|---|---|---|---|---|

| IF | IR <= Memory[PC], PC <= PC + 4 |

同 R 型 | 同 R 型 | 同 R 型 | 同 R 型 | 同 R 型 |

| ID/RF | A <= Reg[IR[25:21]], B <= Reg[IR[20:16]], ALUOut <= PC + (sign-extended(IR[15:0]) << 2) |

同 R 型 | 同 R 型 | 同 R 型 | 同 R 型 | 同 R 型 |

| EX | ALUOut <= A op B |

ALUOut <= A + sign-extend(IR[15:0]) |

同 Load | if (A == B) PC <= ALUOut |

ALUOut <= A op extended(IR[15:0]) |

PC <= {PC[31:28], IR[25:0], 2'b00} |

| MEM | Reg[IR[15:11]] <= ALUOut |

MDR <= Memory[ALUOut] |

Memory[ALUOut] <= B |

- | 同 R 型 | - |

| WB | - | Reg[IR[20:16]] <= MDR |

- | - | - | - |

# 控制信号

多周期处理器中的控制信号及其功能:

| 信号名 | 功能描述 | 备注 |

|---|---|---|

| PCWrite | PC 寄存器常规写入使能 | 0 - 禁用,1 - 启用 |

| PCWriteCond | PC 寄存器条件写入使能 | 0 - 禁用,1 - 启用 |

| PCSource | PC 寄存器写入数据源选择 | 00 - ALU 结果, 01 - ALUOut_reg, 10 - JMP 地址 |

| ALUSrcA | ALU 第一个输入选择 | 0 - PC,1 - RegA |

| ALUSrcB | ALU 第二个输入选择 | 00 - RegB, 01 - 4, 10 - Imm32, 11 - Imm32<<2 |

| ALUOp | ALU 运算类型选择 | add, sub, or 等 |

| RegWrite | 寄存器写入使能 | 0 - 禁用,1 - 启用 |

| RegDst | 写入寄存器选择 | 0 - Rt,1 - Rd |

| MemtoReg | 寄存器写入数据源选择 | 0 - ALU 结果, 1 - 存储器数据 |

| MemRead | 存储器读取使能 | 0 - 禁用,1 - 启用 |

| MemWrite | 存储器写入使能 | 0 - 禁用,1 - 启用 |

| IorD | 存储器地址选择 | 0 - 指令地址,1 - 数据地址 |

| IRWrite | 指令寄存器写入使能 | 0 - 禁用,1 - 启用 |

| EPCWrite | EPC 寄存器写入使能 | 0 - 禁用,1 - 启用 |

| CauseWrite | Cause 寄存器写入使能 | 0 - 禁用,1 - 启用 |

| IntCause | 异常原因选择信号 | - |

# 指令控制信号表

多周期处理器中,不同阶段的控制信号配置:

| 信号名 | IF | ID/RF | EX-R | EX-L/S | EX-B | EX-I | EX-J | MEM-R/I | MEM-L | MEM-S | WB-L |

|---|---|---|---|---|---|---|---|---|---|---|---|

| PCWrite | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 |

| PCWriteCond | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 |

| PCSource | 00 | - | - | - | 01 | - | 10 | - | - | - | - |

| ALUSrcA | 0 | 0 | 1 | 1 | 1 | 1 | - | - | - | - | - |

| ALUSrcB | 01 | 11 | 00 | 10 | 00 | 10 | - | - | - | - | - |

| ALUOp | Add | Add | Func | Add | Sub | Func | - | - | - | - | - |

| RegWrite | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

| RegDst | - | - | - | - | - | - | - | 1 | - | - | 0 |

| MemtoReg | - | - | - | - | - | - | - | 0 | - | - | 1 |

| MemRead | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| MemWrite | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 |

| IorD | 0 | - | - | - | - | - | - | - | 1 | 1 | - |

| IRWrite | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

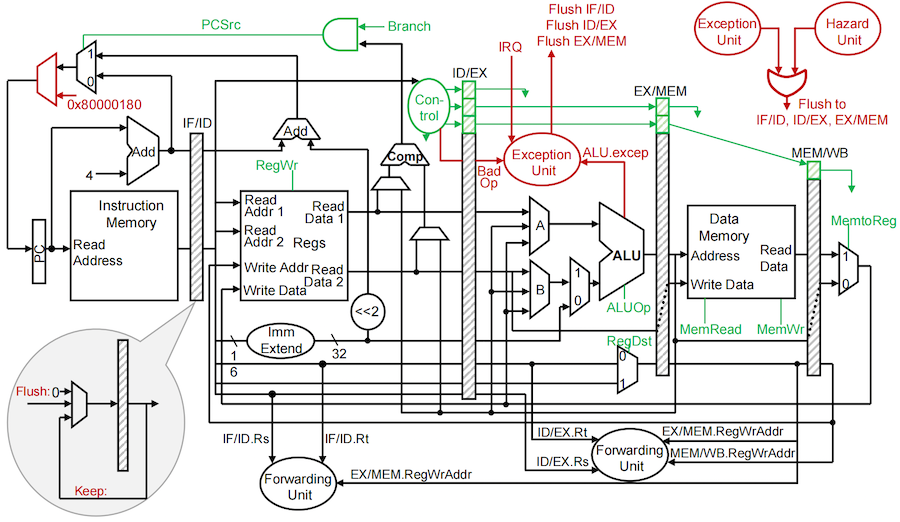

# 流水线处理器设计

# 流水线阶段与级间寄存器

流水线将指令执行分为五个阶段,通过级间寄存器传递数据:

| 阶段 | 级间寄存器 | 功能 | 备注 |

|---|---|---|---|

| IF | IF/ID | 每周期取一条指令,预计算 PC | Instruction Fetch (指令获取) |

| ID/RF | ID/EX | 指令译码,从寄存器堆读取操作数 | Instruction Decode / Register File (指令译码/寄存器堆) |

| EX | EX/MEM | 执行指定的运算,分支跳转 | ALU Execution (ALU 执行) |

| MEM | MEM/WB | 访问存储器 | Memory Data Access (存储器访问) |

| WB | - | 将结果写回寄存器中 | Register Write-Back (寄存器写回) |

# 控制信号

流水线处理器中的控制信号及其作用阶段:

| 信号名 | 功能描述 | 备注 | 作用阶段 |

|---|---|---|---|

| ExtOp | 立即数扩展方式控制 | 0 - 补零,1 - 符号扩展 |

ID/RF |

| ALUSrc | ALU 第二个输入选择 | 0 - regB,1 - imm32 |

EX |

| ALUOp | ALU 运算类型选择 | add, sub, or 等 | EX |

| RegDst | 写入寄存器选择 | 0 - Rt,1 - Rd |

EX |

| MemWr | 存储器写入使能 | 0 - 禁用,1 - 启用 |

MEM |

| Branch | 是否是 beq 指令 | 0 - 不是,1 - 是 |

MEM |

| MemtoReg | 寄存器写入数据源选择 | 0 - ALU 结果,1 - 存储器数据 |

WB |

| RegWr | 寄存器写入使能 | 0 - 禁用,1 - 启用 |

WB |