# 基本概念

# 时钟与同步

-

时钟生成

- 环形振荡器: 由奇数个反相器首尾相连组成。其周期为反相器个数与单个反相器延迟乘积的两倍。

-

时钟触发

- 边缘采样: 时序电路在时钟信号的上升沿或下降沿对输入信号进行采样,以更新其内部状态。

-

时钟域

- 同步: 指信号的事件发生与时钟的节拍严格保持一致。

- 时钟域: 指所有同步于同一个时钟信号的信号集合。

# 有限状态机 (FSM)

-

定义: 一种抽象的数学模型,用于描述一个系统在特定输入下如何从一个状态转移到另一个状态,并产生相应输出。

-

六大要素:

- 状态(State): 系统的当前情况。

- 输入(Input): 外部信号。

- 输出(Output): 系统的响应。

- 状态转移函数 : 决定下一个状态。

- 输出函数 : 决定当前输出。

-

FSM 分类

- 摩尔机(Moore): 输出只与当前状态有关。

- 米利机(Mealy): 输出与当前状态和当前输入都有关。

-

FSM 描述方法

- 状态转换表

- 摩尔机: 表格包含“当前状态”、“输入下的次态”和“对应输出”三列。

- 米利机: 表格包含“当前状态”和“输入下的次态及对应输出”两列。

- 状态图

- 摩尔机: 每个状态用一个圆圈表示,圆圈内部标记状态和该状态下的输出。箭头标记引起状态转移的输入。

- 米利机: 每个状态用一个圆圈表示,圆圈内部只标记状态。箭头标记引起状态转移的输入和该输入下产生的输出,格式为 “输入/输出”。

- 状态转换表

# 存储单元:锁存器与触发器

# 锁存器(Latch)

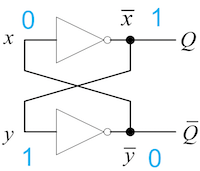

- 基本概念: 一种能够存储 1 bit 状态的双稳态单元。

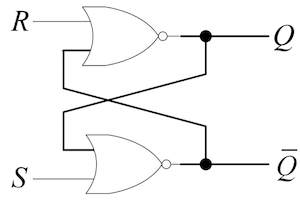

- SR 锁存器

- 功能: 由两个交叉耦合的非门或或非门组成,可实现“置位(Set)”、“复位(Reset)”和“保持”功能。

- 特征方程: 。

- 功能真值表:

| S | R | 功能 | |

|---|---|---|---|

| 0 | 1 | 0 | 复位 |

| 1 | 0 | 1 | 置位 |

| 0 | 0 | Q | 保持 |

| 1 | 1 | 不允许 |

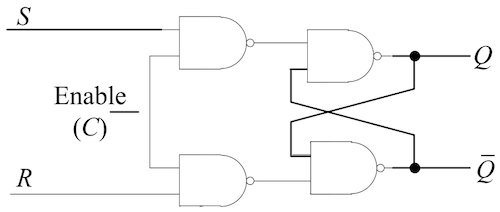

- 门控 SR 锁存器

- 功能: 增加了使能信号 C,只有当 C=1 时才能改变状态。

- 特征方程: 。

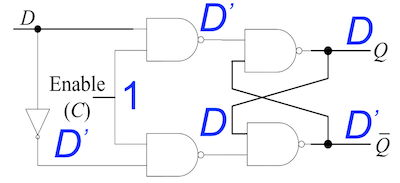

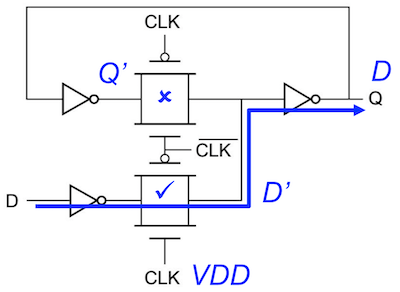

- 门控 D 锁存器

- 功能: 当使能信号 C 为高电平时,输出 Q 跟踪输入 D。当 C 变为低电平时,输出被锁定在最后的值。

- 特征方程: 。

- 时序参数

- 最小脉冲宽度 (): 保证输入信号有效所需的最短时间。

- 延迟 (): 从输入变化到输出变化所需的时间。

- 建立时间 (): 时钟有效沿到来之前,输入信号必须保持稳定的最短时间。

- 保持时间 (): 时钟有效沿到来之后,输入信号必须保持稳定的最短时间。

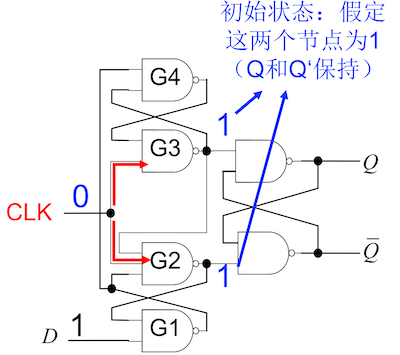

# D 触发器(DFF)

- 基本概念: D 触发器与门控 D 锁存器的区别在于其符号中 C 处有一个缺口,表示其为边沿触发。

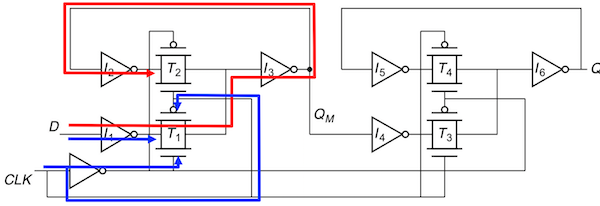

- 结构: 典型的 D 触发器采用主从(Master-slave)结构。

- 主级锁存器在时钟高电平时跟随输入,从级锁存器在时钟低电平时跟随主级。

- 整体上,输出在时钟上升沿时更新,并保持不变,直到下一个上升沿。

- 主从结构时序参数:

- 建立时间: 取决于信号从输入端 D 传输到主级锁存器 I2 所需的时间。

- 保持时间: 保持时间原生满足。

- 延迟: 取决于信号从主级传输到从级再到输出端所需的时间 ()。

- 描述方式:

- 真值表: 描述在不同输入和时钟沿下,输出的变化。

- 状态图: 描述状态间的转移。

- 特征方程: 描述下一状态与当前状态和输入之间的代数关系。

- 激励表: 描述要实现某种状态转移,需要什么样的输入。

# 其他类型触发器

- T 触发器(TFF): 当输入 T=1 时,状态翻转;当 T=0 时,状态保持不变。

- 特征方程: 。

- JK 触发器(JKFF): 是一种通用的触发器。

- 当 J=K=0 时,保持;当 J=K=1 时,翻转。

- 当 J=1, K=0 时,置位;当 J=0, K=1 时,复位。

- 特征方程: 。

- RS 触发器(RSFF): 类似于门控 SR 锁存器,但其状态改变是由时钟的上升沿触发。

- 特征方程: 。

# 同步时序电路分析与设计

# 电路分析

-

分析步骤

- 电路分析: 导出输出方程、激励方程和状态转移函数。

- 行为分析: 根据状态转移函数,创建状态转移表、状态图,并分析电路的时序行为。

-

摩尔机与米利机对比

- 摩尔机: 输出变化与状态变化同步。

- 米利机: 输出是输入和状态的组合逻辑,输出变化与状态和输入的变化异步。

-

关键路径: 寻找延时最长的逻辑路径,以确定电路的最高工作频率。

# 电路设计

-

设计步骤

- 抽象 FSM: 定义初始状态、系统输入/输出,并建立状态转移关系,判断其为摩尔机还是米利机。注意,输出不参与状态分配。

- 状态化简:

- 行匹配: 找出并合并具有相同次态和输出的行,重复该过程直到无法再合并。

- 蕴含表: * 构造蕴含表。

- 根据输出是否相同,标记不可等价的“x”。

- 根据次态和输出,标记等价的“√”。

- 对于剩余的单元,填入等价条件,并逐一检查条件,不满足时标记“x”。

- 状态分配: 用二进制 0/1 对状态进行编码。

- 随机编码: 无特定规则。

- 顺序编码: 如二进制加法计数顺序或格雷码顺序。

- 独热编码: 每个状态都用一个 N 位二进制码表示,且只有一位为 1。

- 面向输出的编码: 倾向于将输出相同的状态编码为相邻。

- 启发式方法: 旨在减少触发器之间的连接数量和功耗。

- 高优先级: 当输入相同时,次态相同的状态应具有相邻编码。

- 中优先级: 同一状态的不同次态应具有相邻编码。

- 低优先级: 具有相同输出的状态应具有相邻编码。

- 确定方程: 导出激励方程和输出方程。

- 绘制电路图: 根据方程画出逻辑电路图。

-

应用举例

- 移位寄存器: 包括右移、左移和双向移位寄存器。

- 串行输入/输出 vs. 并行输入/输出: 并行输入允许在一个时钟周期内同时加载一组新值。

- 计数器: * 加法/减法计数器、特殊进制计数器: 需要考虑自启动问题,确保计数器能从任意非指定状态回到正常计数序列。

- 环形计数器: 由 N 个触发器构成,可表示 N 个不同状态。

- 扭环形计数器(Johnson Counter): 由 N 个触发器构成,可表示 2N 个不同状态。

- 异步计数器: * 能表示所有状态。

- 最低位触发器 必须翻转。

- 高位触发器 是否翻转,取决于所有低位触发器的状态是否都为 1。

- 同步计数器: * 能表示所有状态。

- 利用 的翻转规则(取决于所有低位触发器的状态是否为 1)来设计。

- 在设计时需要平衡速度和面积。

- 移位寄存器: 包括右移、左移和双向移位寄存器。